# Split-Capacitor Five-Level Transformerless Grid Connected Single Phase PV System using Level Shifted PWM Technique

## P. Manikandan<sup>1</sup>, P. Maruthupandi<sup>2</sup>

<sup>1</sup>Research Scholar, Dept. of Electrical and Electronics Engineering, Government College of Technology, Coimbatore

<sup>2</sup>Assistant Professor, Dept. of Electrical and Electronics Engineering, Government College of Technology, Coimbatore

E-mail: 1manikandan.p.eee@gmail.com, 2pandi@gct.ac.in

#### **Abstract**

This paper proposes Level shifted Pulse Width Modulation (PWM) methods for single phase transformerless Multi Level Inverter (MLI). Many of the existing topologies have high variations in Common Mode Voltage (CMV) and high leakage current. The proposed topology with level shifted PWM technique for five level single phase MLI, reduces the variations in CMV, minimizes the leakage current according to VDE0126-1-1 standard and the reduced number of switches makes the losses less than the conventional topologies. This topology reduces the current THD. Finally, simulations are carried in MATLAB/Simulink for different inverter topologies.

**Keywords:** Level Shifted PWM, single phase Multi Level transformer less inverter topologies, Leakage current reduction, Common Mode Voltage

## 1. Introduction

The increasing in energy demand is most addressed problem in recent days due to increasing population and increasing of electrical applications like electric vehicles. Renewable energy sources play a major role to meet out the energy demand. Anzalchi *et al.* 2017 stated that solar PV is rapidly increasing renewable sectors compare with other sectors [1]. According to International (IEA), solar PV is the third highest renewable power generation after overtaking bioenergy in 2019, solar power generation increased to 156 TWh, which is 23 % higher than 2019 solar power generation. Grid connected PV inverters are basically classified as inverter with transformer and inverter without transformer. Inverter

with transformer provides step up and step-down operation and electrical isolation. Inverter without transformer causes the leakage current issues; which does not provide the step up and step down operation to the system [2].

Different inverter topologies are proposed with many PWM techniques to maintaining the CMV as constant and to reduce the leakage current. Freddy et al. 2015, developed H-7 inverter topology with DPWM to reduce the leakage current. This topology reduces the leakage current significantly but it has the high variation in common mode voltage. Rath et. al 2018 developed stored energy modulation with eight switch transformerless inverter. This topology completely eliminates the leakage current and maintain the common mode voltage as constant. However, this topology is complexity in filter design and does not provide the voltage linearity.

Siwakoti et al., 2018, discussed NPC based Multi Level Inverter [3]. This topology reduces the leakage current considerably. But this topology does not provide reactive power capability and high number switches causes lower efficiency in the overall system due to high switching losses. Hava et al. 2009, discussed ten switch non isolated single-phase inverter with SPWM. This topology suppresses the leakage current considerably. Main drawback of the system is reactive power capability and requirement of modified filter design. Li et al. 2019, discussed current source AC decoupling inverter with discontinues PWM transformerless inverter. In addition to leakage current this topology maintains the input voltage constant. but this fails to ensure the reactive power capability and requires additional filter elements in grid side [4].

Ashadi et. al 2020, discussed voltage source T type inverter with modified discontinues PWM technique. This topology ensures the common mode voltage along low switching losses due selecting vector methodology. but this system requires additional input DC link capacitor. Guo et. al 2019, analyzed single phase DC bypass clamped topologies with unclamped DC bypass topologies [5]. Suganthi et. al 2021, discussed about the leakage current reduction in three phase H7 inverter [6]. This analysis stated that unclamped topologies provide better efficiency than clamped topologies in terms of leakage current and common mode voltage. This proposed topology with DC clamping switches used to minimize the variations in common mode Voltage. Level shifted PWM used to reduce the grid current THD and proposed topology helps to reduce leakage current.

This paper has organized as following, Section 1 discusses about the related literature studies. Section 2 analyzes proposed five level transformerless inverter with Level shifted PWM technique switching states. In Section 3 bases on the simulation analysis of proposed topologies. The conclusion is dicussed in Section 4.

## 2. Proposed Topology with Level Shifted Pulse Width Modulation Technique

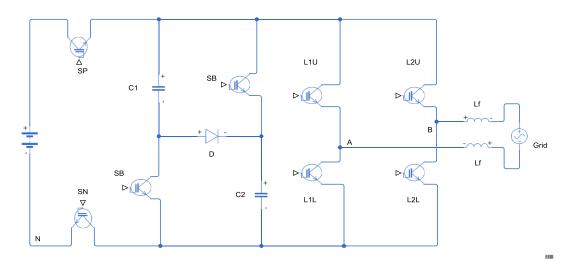

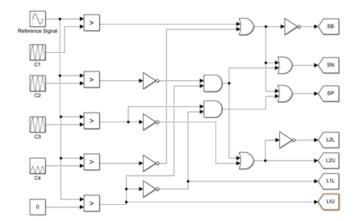

The improved five-level single phase transformerless inverter structure is shown in Figure 1. During normal operating condition the inverter act as conventional inverter. The DC clamping circuit is continuously in ON state. During zero voltage state the DC clamping circuits isolates the grid and PV panel and is in OFF state; This circuit is used to maintains the common mode voltage as fixed. The proposed Level shifted PWM technique is given in figure 2a.

Figure 1. Proposed Five Level Transformerless MLI

Figure 2a. Proposed Level Shifted PWM switching pattern

ISSN: 2582-337X 42

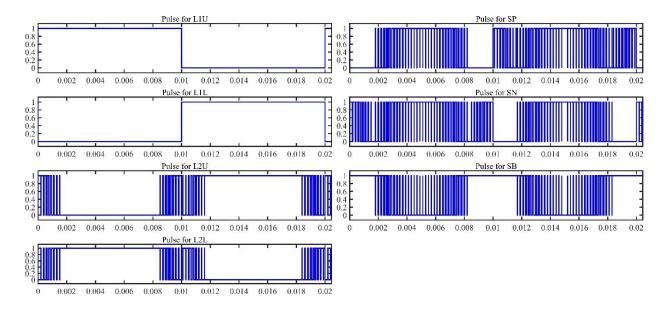

Required pulse of the switches are generated by the combination of the signal as shown in figure 2b.

Figure 2b: Generated Pulse for the proposed MLI

The variations of common mode voltage is given in table 1. The CMV varies is constant at  $V_{DC}/2$ . In existing MLI topology the CMV varies between  $V_{DC}/4$  to  $3V_{DC}/4$ . This causes the high leakage current in the system.

Vo  $V_{CMV}$ L1U L1L L2U L2L SP SB SNVdc  $V_{DC}/2$ Vdc/2  $V_{DC}/2$  $V_{DC}/2$ 0+  $V_{DC}/2$ 0-Vdc/2  $V_{DC}/2$  $V_{DC}/2$ Vdc

**Table 1**. Switching table for proposed inverter

Table 2. Specification

10050 Hz

| Fundamental frequency | 50 Hz   |

|-----------------------|---------|

| Grid Voltage          | 230 V   |

| Rated Power           | 2.5 kW  |

| Filter Inductor       | 8 mH    |

| Capacitor C1, C2      | 2200 μF |

$10 \Omega$

100 nF

TS250 -10 panels

## 3. Simulation Results and Discussion

PV Panel

Switching frequency

Parasitic resistance

Parasitic capacitance

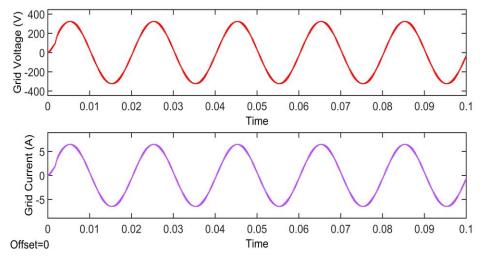

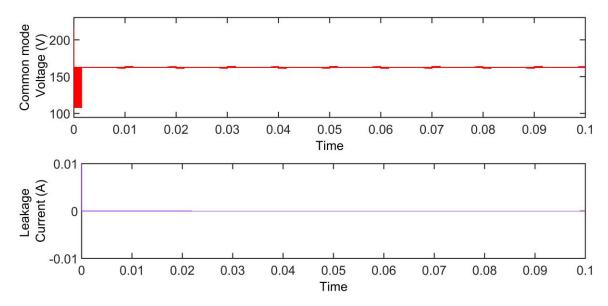

The proposed topology simulations is carried out in MATLAB/Simulink. Figure 4 (a) shows the grid voltage waveform of proposed methodology. Figure 4 (b) depicts the grid current waveform of proposed method. Simulated results of CMV and Leakage Current (I leak) of proposed MLI are shown in figure 4.

**Figure 3.** Simulated results of the proposed topology (a) Grid Voltage waveform (b) Grid Current waveform

ISSN: 2582-337X 44

Figure 4. Simulated waveforms of the proposed topology

(a) Common-Mode Voltage (CMV) (b) Leakage Current (I leak)

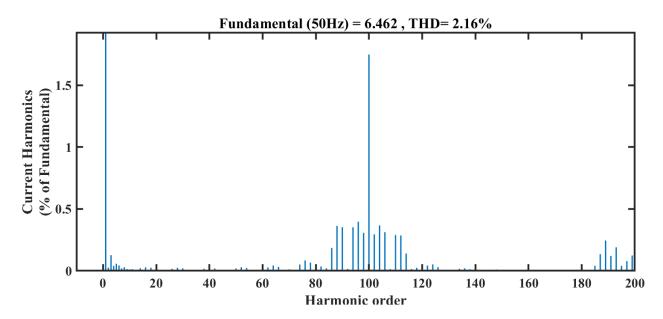

The Common Mode Voltage (CMV) of the proposed topology portrays in figure 4 (a). the leakage current ( $I_{leak}$ ) of proposed topology portrays at figure 4 (b). Figure 5 shows the THD of grid current of proposed inverter topology.

Figure 5. Grid Current THD Profile for the proposed inverter

The stray capacitor voltage differences are maintaining the DC link Voltage as 160 V in MLI topology. Injecting grids current THD is 2.16 %. For this case, leakage current is maintained at zero which is allowable level of 300 mA as mentioned in standard VDE 0126-1-1. Which is acceptable parameter for connecting the inverter to grid without transformer.

### 4. Conclusion

In this paper, a single phase improved five-level MLI with Level shifted PWM for grid-connected transformerless photovoltaic systems is proposed to eliminate the leakage current. The proposed system is simulated on the MATLAB/SIMULINK platform. The improved DC side clamping inverter is proposed with Level shifted PWM topology which isolates the Photovoltaic system from the grid during zero voltage stage and provides the path for leakage current (I<sub>leak</sub>). Also, the number of switches used for five level inverter is minimum in this case, which reduces the losses associated with switching. Simulation results show that the leakage current in the improved five level MLI is found to be zero, which is lower than the existing single phase Multi Level Inverter topology. Based on grid current harmonics injected and leakage current values, the improved five-level single phase transformerless inverter topology provides better performance.

#### References

- [1] M. Islam, S. Mekhilef, and M. Hasan, "Single phase transformerless inverter topologies for grid-tied photovoltaic system: A review," Renewable and Sustainable Energy Reviews, vol. 45, pp. 69 86, 2015

- [2] Siwakoti, Yam P., and Frede Blaabjerg. "Common-ground-type transformerless inverters for single-phase solar photovoltaic systems." IEEE Transactions on Industrial Electronics 65.3 (2017): 2100-2111.

- [3] L. Zhou, F. Gao, and T. Xu, "A family of neutral-point-clamped circuits of single-phase pv inverters: Generalized principle and implementation," IEEE Transactions on Power Electronics, vol. 32, no. 6, pp. 4307–4319, 2016.

- [4] Reza Barzegarkhoo, Yam P. Siwakoti, Teng Long, and Frede Blaabjerg, "Five-Level Grid-Tied Inverter Employing Switched Capacitor Cell with Common-Grounded Feature", IEEE Transactions on Power Electronics, 2020.

- [5] L. Zhou, F. Gao and T. Xu, "Implementation of Active NPC Circuits in Transformer-Less Single-Phase Inverter with Low Leakage Current", IEEE Transactions on Industry Applications, vol. 53, no. 6, pp. 5658-5667, Nov.-Dec. 2017

ISSN: 2582-337X 46

[6] Suganthi Ramasamy, and Maruthupandi Perumal. "CNN-based deep learning technique for improved H7 TLI with grid-connected photovoltaic systems." International Journal of Energy Research 45.14 (2021): 19851-19868.

## Author's biography

- **P. Manikandan** received his Bachelor of Engineering in Electrical and Electronics Engineering from Kalaignar Karunanidhi Institute of Technology, Coimbatore, India and Master of Engineering degree in Power Electronics and Drives from Bannari Amman Institute of Technology, Tamil Nadu, India. He has a 5 years of teaching experience. He is presently pursuing his doctorial degree in Electrical Engineering, Anna University. His area of interest includes power converters design, Renewable Energy, Electric Vehicles.

- **P. Maruthupandi** has received Bachelor degree in Electrical and Electronics Engineering from Government College of Engineering, Tamil Nadu in 1995 and Master degree in Power Electronics and Drives from College of Engineering, Chennai, India in 2002 and Ph.D., degree from Anna University, Chennai in the year 2012. He has over 22 years of experience in teaching. He is currently working as Assistant Professor in the Department of Electrical Engineering of Government College of Technology, Coimbatore, India. His field of interests includes power electronics and electrical drives, power quality, simulation of power converters and Electrical Vehicle.